## Full Chip Modelling of ICs under CDM Stress

Sheela Sowariraj

9 June, 2005

#### Samenstelling van de promotiecommissie

Voorzitter: prof.dr.ir. J. van Amerongen University of Twente

Promotor: prof.dr.ir. F.G. Kuper University of Twente/Philips

Assistent-promotor: prof.dr.ir. A.J. Mouthaan University of Twente

Leden: dr.ir. T. Smedes Philips Semiconductors

prof.dr.ir. G. Groeseneken

prof.dr. J. Schmitz

University of Twente

prof.dr.ir. F.B.J. Leferink

University of Twente

This research was done in the MESA+ research institute/University of Twente, The Netherlands and was funded by Philips Semiconductors, Nijmegen, The Netherlands.

Title: Full Chip Modelling of ICs under CDM Stress

Author: Sheela Sowariraj

ISBN: 90-365-2217-x (print)

ISBN: 90-365-2217-x (PDF)

Copyright © 2005 by Sheela Sowariraj, Enschede, The Netherlands

No part of this work may be reproduced by print, photocopy or any other means without the permission in writing from the publisher.

Publisher: PrintPartners Ipskamp, Enschede, The Netherlands

#### FULL CHIP MODELLING OF ICs UNDER CDM STRESS

#### **PROEFSCHRIFT**

ter verkrijging van

de graad van doctor aan de Universiteit Twente,

op gezag van de rector magnificus,

prof.dr. W.H.M. Zijm,

volgens besluit van het College voor Promoties

in het openbaar te verdedigen

op donderdag 9 juni 2005 om 13.15 uur

door

Mary Sheela Bobby Sowariraj geboren op 12 september 1977 in Pondicherry, India Dit proefschrift is goedgekeurd door de promotor prof.dr.ir. F.G. Kuper en de assistent-promotor prof.dr.ir. A.J. Mouthaan

# Contents

| Summary              |                     |                                         | 1  |

|----------------------|---------------------|-----------------------------------------|----|

| Sa                   | menv                | ratting                                 | 3  |

| 1                    | Introduction        |                                         |    |

|                      | 1.1                 | ESD in Semiconductor Industry           | 8  |

|                      | 1.2                 | ESD Protection Design                   | 11 |

|                      | 1.3                 | ESD Characterization Methods            | 13 |

|                      |                     | 1.3.1 Transmission Line Pulse           | 14 |

|                      |                     | 1.3.2 Very fast Transmission Line Pulse | 15 |

|                      | 1.4                 | Scope of this Thesis                    | 16 |

|                      | 1.5                 | Thesis Outline                          | 17 |

| 2                    | IC under CDM Stress |                                         |    |

|                      | 2.1                 | Introduction                            | 19 |

| 2.2 CDM in real-life |                     | CDM in real-life                        | 20 |

|                      | 2.3                 | Failure encountered from CDM Stress     | 22 |

|                      | 2.4                 | CDM Test Methods                        | 22 |

|                      |                     | 2.4.1 Non-Socketed Test Method/CDM      | 22 |

|                      |                     | 2.4.2 Socketed Test Method              | 25 |

| 2.5 Need for CDM Simulation |                           |                                             | 25                                   |    |

|-----------------------------|---------------------------|---------------------------------------------|--------------------------------------|----|

|                             |                           | 2.5.1                                       | Requirements for CDM Circuit Model   | 26 |

|                             | 2.6                       | 6 CDM circuit simulation - State-of-the-art |                                      |    |

|                             |                           | 2.6.1                                       | Previous Chip Level Circuit Model    | 27 |

|                             |                           | 2.6.2                                       | Proposed CDM Model                   | 28 |

|                             | 2.7                       | Conclu                                      | asions                               | 31 |

| 3                           | <b>Protection Devices</b> |                                             |                                      |    |

|                             | 3.1                       | Introdu                                     | uction                               | 33 |

|                             | 3.2                       | Device                                      | physics                              | 34 |

|                             |                           | 3.2.1                                       | Diodes                               | 34 |

|                             |                           | 3.2.2                                       | ggMOSt                               | 36 |

|                             | 3.3                       | Measu                                       | rements                              | 41 |

|                             |                           | 3.3.1                                       | ggNMOSt                              | 41 |

|                             |                           | 3.3.2                                       | LVTSCRt                              | 43 |

|                             |                           | 3.3.3                                       | Failure analysis                     | 45 |

|                             | 3.4                       | Simula                                      | ations                               | 46 |

|                             |                           | 3.4.1                                       | Compact Circuit Model for ggNMOSt    | 46 |

|                             |                           | 3.4.2                                       | Model Validation from TLP and vf-TLP | 49 |

|                             |                           | 3.4.3                                       | Compact Model of MOSt                | 55 |

|                             | 3.5                       | Conclu                                      | asions                               | 55 |

| 4                           | I/O                       | Protecti                                    | ion Circuits                         | 57 |

| 4.1 Introduction            |                           | action                                      | 57                                   |    |

|                             |                           | 4.1.1                                       | Input Protection Design              | 58 |

|                             |                           | 4.1.2                                       | Output Protection Design             | 62 |

|                             | 4.2                       | Measu                                       | rements                              | 63 |

|                             |                           | 4.2.1                                       | Description of test structure        | 63 |

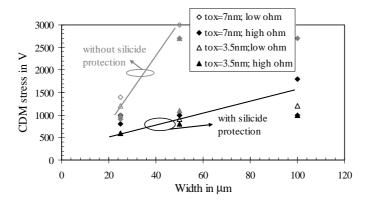

|                             |                           | 4.2.2                                       | CDM Stress and Failure Diagnosis     | 64 |

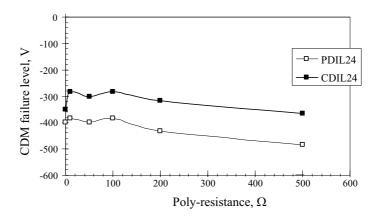

|                             |                           | 4.2.3                                       | Results and Discussions              | 64 |

|                 |                       | 4.2.4                                        | Failure Analysis                                         | 67         |  |  |

|-----------------|-----------------------|----------------------------------------------|----------------------------------------------------------|------------|--|--|

| 4.3 Simulations |                       |                                              | ations                                                   | 69         |  |  |

|                 |                       | 4.3.1                                        | Input Protection Design                                  | 69         |  |  |

|                 |                       | 4.3.2                                        | Output Protection Design                                 | 75         |  |  |

|                 | 4.4                   | Conclu                                       | usions                                                   | 77         |  |  |

| 5               | Pacl                  | kage In                                      | fluence                                                  | <b>7</b> 9 |  |  |

|                 | 5.1                   | Introduction                                 |                                                          |            |  |  |

|                 | 5.2                   | 5.2 Package capacitance - CDM current source |                                                          |            |  |  |

|                 |                       | 5.2.1                                        | Correlation of failure level to discharge current        | 83         |  |  |

|                 | 5.3                   | Propos                                       | sed Package Calibration Method                           | 86         |  |  |

|                 |                       | 5.3.1                                        | Validation of the Proposed Method                        | 87         |  |  |

|                 | 5.4                   | Conclu                                       | usions                                                   | 90         |  |  |

| 6               | Substrate Influence 9 |                                              |                                                          |            |  |  |

|                 | 6.1                   | Introduction                                 |                                                          |            |  |  |

|                 | 6.2                   | Signifi                                      | icance of $C_{\mathrm{SUB}}$                             | 94         |  |  |

|                 |                       | 6.2.1                                        | $C_{\text{SUB}}$ , Major CDM current source              | 94         |  |  |

|                 |                       | 6.2.2                                        | Distributed discharge current path of $C_{\mathrm{SUB}}$ | 96         |  |  |

|                 | 6.3                   | Circui                                       | t model for substrate                                    | 98         |  |  |

|                 |                       | 6.3.1                                        | Existing substrate models                                | 98         |  |  |

|                 |                       | 6.3.2                                        | Substrate model applicable for CDM event                 | 98         |  |  |

|                 |                       | 6.3.3                                        | Circuit model for MOS                                    | 100        |  |  |

|                 |                       | 6.3.4                                        | Simplifications on the model                             | 100        |  |  |

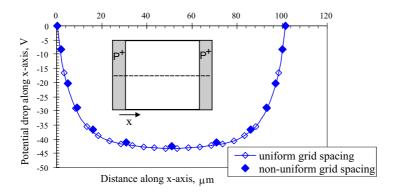

|                 |                       | 6.3.5                                        | Simulation Difficulties                                  | 102        |  |  |

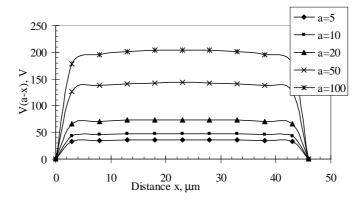

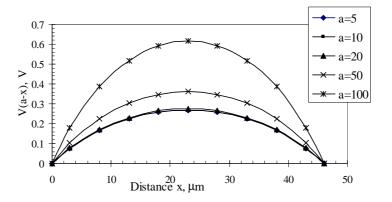

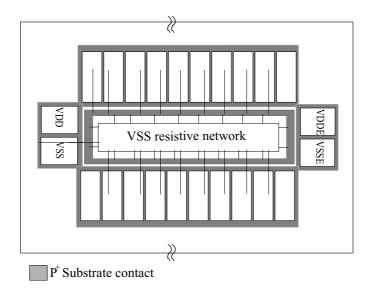

|                 | 6.4                   | The di                                       | stribution of substrate contacts                         | 102        |  |  |

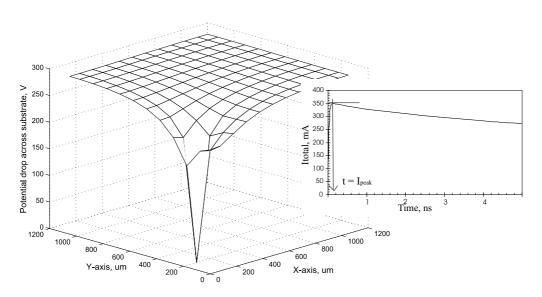

|                 |                       | 6.4.1                                        | Single substrate contact                                 | 103        |  |  |

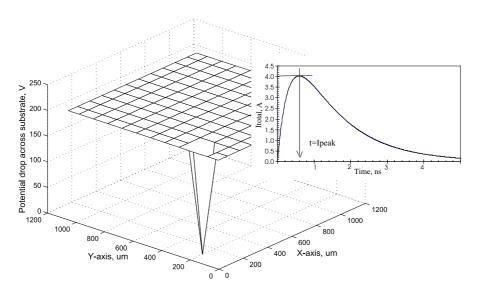

|                 |                       | 6.4.2                                        | A ring of substrate contacts                             | 106        |  |  |

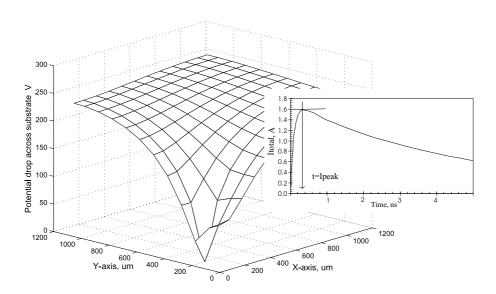

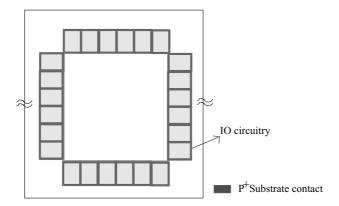

|                 |                       | 6.4.3                                        | Substrate contact distribution in realistic case         | 108        |  |  |

|                 |                       | 6.4.4                                        | Meshing Criteria                                         | 111        |  |  |

|                                         | 6.5                         | Conclu                         | usions                           | 112 |  |  |

|-----------------------------------------|-----------------------------|--------------------------------|----------------------------------|-----|--|--|

| 7                                       | Full Chip Circuit Model - 1 |                                |                                  |     |  |  |

|                                         | 7.1                         | Introd                         | uction                           | 115 |  |  |

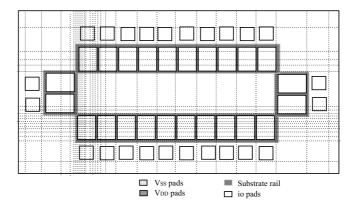

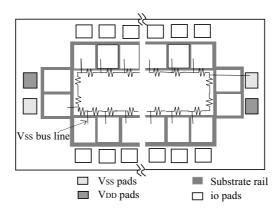

|                                         |                             | 7.1.1                          | IC Description                   | 116 |  |  |

|                                         |                             | 7.1.2                          | CDM Measurement Results          | 118 |  |  |

|                                         |                             | 7.1.3                          | Discussion                       | 118 |  |  |

|                                         | 7.2                         | Buildi                         | ng of the 3D Circuit model       | 120 |  |  |

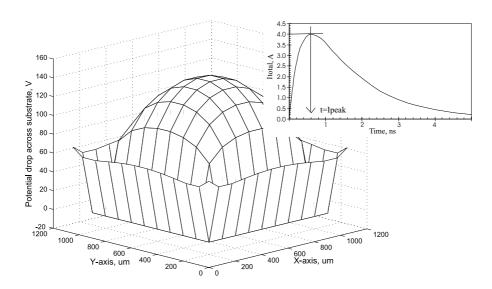

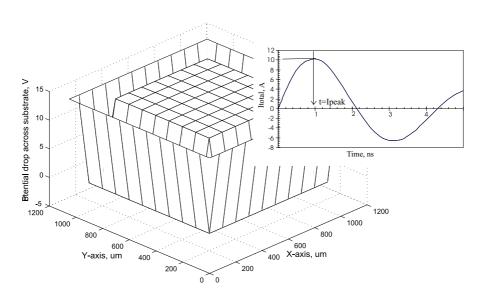

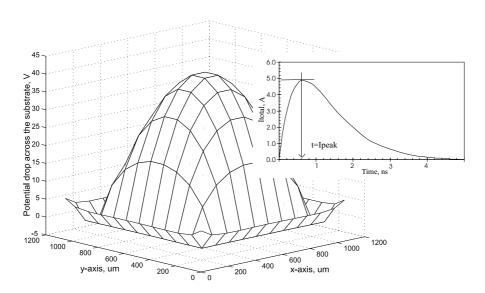

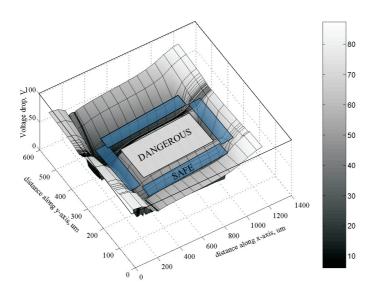

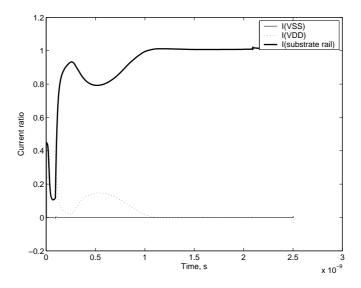

| 7.3 Voltage transients across substrate |                             | ge transients across substrate | 122                              |     |  |  |

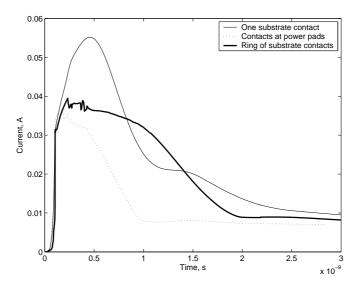

|                                         |                             | 7.3.1                          | One Contact                      | 124 |  |  |

|                                         |                             | 7.3.2                          | Contacts at power pads           | 129 |  |  |

|                                         |                             | 7.3.3                          | Ring of substrate contacts       | 131 |  |  |

|                                         | 7.4                         | Conclu                         | usions                           | 135 |  |  |

| 8 Full Chip Circuit Model - 2           |                             |                                | Circuit Model - 2                | 137 |  |  |

|                                         | 8.1                         | Introd                         | uction                           | 137 |  |  |

|                                         |                             | 8.1.1                          | IC Description                   | 138 |  |  |

|                                         |                             | 8.1.2                          | CDM Measurements and Results     | 138 |  |  |

|                                         |                             | 8.1.3                          | Discussion                       | 139 |  |  |

| 8.2 Building of the 3D circuit model    |                             | Buildi                         | ng of the 3D circuit model       | 141 |  |  |

|                                         | 8.3                         | Voltag                         | ge transients across the Circuit | 143 |  |  |

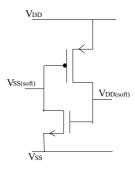

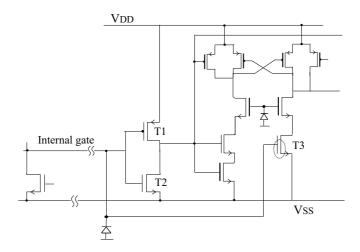

| 8.4 Level Shifter Circuit               |                             | Shifter Circuit                | 144                              |     |  |  |

|                                         |                             | 8.4.1                          | One contact                      | 145 |  |  |

|                                         |                             | 8.4.2                          | Contact at each I/O pin location | 148 |  |  |

|                                         |                             | 8.4.3                          | Smaller guard ring area          | 151 |  |  |

|                                         | 8.5                         | Tie-Of                         | ff Cell                          | 151 |  |  |

|                                         |                             | 8.5.1                          | One contact                      | 153 |  |  |

|                                         |                             | 8.5.2                          | Contact at each I/O pin location | 155 |  |  |

|                                         |                             | 8.5.3                          | Smaller guard ring area          | 157 |  |  |

|                                         | 8.6                         | Conclu                         | usions                           | 158 |  |  |

|                 | Contents |

|-----------------|----------|

| Conclusions     | 159      |

| Acknowledgement | 163      |

| Bibliography    | 165      |

## Summary

From the day of the invention of the first transistors until today, the size of the transistors used in the electronic integrated circuits (ICs) has been reduced drastically. With reducing device dimensions, the capability to withstand high voltages across the circuits has also been decreasing. When an IC is subjected to Electrostatic Discharge (ESD), a large current flows from the static charge source to the grounded pin through the circuit. To protect the circuits from being damaged by ESD, large protection devices capable of handling large currents are built into the circuit to provide low impedance paths for the discharge current. During packaging, marking or shifting, ICs can build up static charge due to rubbing of surfaces. When such charged ICs touch a grounded surface, Charged Device Model (CDM) type of ESD is said to occur. The increased usage of automated handlers increases the probability of ICs being subjected to CDM stress, while the scaling down of device dimensions cause the ICs to be vulnerable to CDM damage.

In this thesis, CDM ESD stress on the Integrated Circuits (IC) and the various factors which affect the robustness of an IC design against CDM stress is investigated. One of the main reasons for CDM failure are the voltage gradients set across the circuit during CDM stress. The IC being also the source, its discharge current path is not constrained near the input and output pads as in other kinds of ESD stress. Instead it can be anywhere through the internal circuitry into the ground. The major hinderance in developing a CDM robust protection design is the lack of knowledge on the CDM current and its discharge path through the circuit. CDM withstand level, is package dependent and it is impossible to characterize a circuit design to be CDM robust independent of its package type.

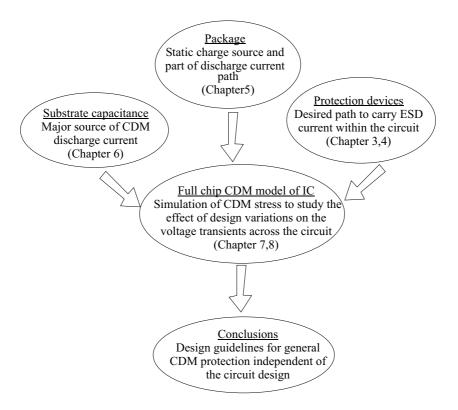

In **chapter two**, the CDM current source is identified and an equivalent circuit model for an IC under CDM stress is proposed.

Protection devices are key elements of any ESD protection. The behavior of some of the commonly used protection devices under fast transient large current CDM stress is studied in **chapter three**.

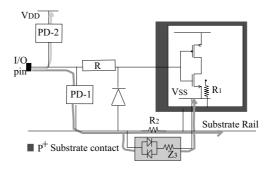

The input and output buffers form an interface between the outside world and inside core circuit. Hence these circuits at this interface are one of the most vulnerable locations to CDM failure. The CDM guidelines available in the literature recommend the use of large resistors between the protection device and the circuit to be protected. Placement of additional protection devices closer to the device to be protected is also recommended. In **chapter four**, the individual influence of each of these design variations and their effect on the current and voltage transients across the input and out buffers is studied.

The package type plays a significant role in the CDM failure level of a device. As a result, CDM measurements on the same circuit design has to be repeated each time the package type is changed. This consumes a large amount of time and money. In **chapter five**, a suitable method for extrapolating the CDM withstand level of a circuit in one package to other packages. The proposed method is also experimentally verified. This method does require extensive and accurate measurements of the package parasitics.

Among the various CDM current sources, the capacitance formed by the metal plate on which the IC chip is mounted, with the ground surface is the largest. The discharge current path of this capacitor is through the substrate and the circuits into the grounded pin. This discharge causes voltage drop across the substrate and circuit elements (e.g gates). If the voltage drop increases beyond a certain threshold (gate-oxide breakdown voltage), CDM failure is said to occur. The probability of CDM damage from such voltage drops cannot be determined from the existing full-chip CDM circuit model. In **chapter six**, a suitable method of including this capacitance and its discharge current path through the substrate and the circuit during CDM stress is presented.

The application of the proposed method in chapter five, on three different circuit designs (input protection, tie-off cell and level-shifter) is presented in **chapter seven** and **chapter eight**. Chapter seven focusses on pad based protection design and chapter eight on rail based protection design.

## Samenvatting

Vanaf de uitvinding van de transistor tot vandaag de dag zijn de afmetingen van transistoren in geïntegreerde schakelingen (IC) drastisch gereduceerd. Hand in hand daarmee is ook het stroomvoerende vermogen van het circuit afgenomen. Wanneer een IC wordt blootgesteld aan één ontlading van statische elektriciteit (ESD) dan gaat er een grote stroom door het circuit lopen van de statische ladingsbron naar een van de geaarde pootjes van het IC. Om het circuit te beschermen tegen de schade die veroorzaakt kan worden door een dergelijke ontlading worden er beschermingselementen ingebouwd. Deze elementen zijn in staat om grote stomen te voeren en vormen een pad van lage impedantie voor de ontlaadstroom.

Tijdens verschillende fases in het fabricage-proces, zoals tijdens behuizen en tijdens markeerstappen, kunnen IC's door wrijving worden opgeladen. Indien een opgeladen IC daarna in aanraking komt met een geaard oppervlak volgt een elektrostatische ontlading van het type "Charged Device Model (CDM)". Door de toegenomen automatisering van transport van halfgeleider-halffabrikaten en ingehuisde IC's is de kans op CDM-stress verhoogd. Daarnaast verhoogt miniaturisatie van het IC kwetsbaarheid voor CDM-schade.

Dit proefschrift onderzoekt de effecten van CDM-ESD-stress op geïntegreerde circuits (IC) en de diverse factoren die een rol spelen in de robustheid van een IC-ontwerp om een CDM-stress te weerstaan. Een van de belangrijkste oorzaken waardoor IC's als gevolg van CDM-stress falen is de gradiënt in de potentiaal over het circuit gedurende de CDM-stress. Omdat het IC zelf de ladingsbron is, wordt het ontladingspad niet beperkt tot de invoer- en uitvoer-aansluitingen, maar kan de stroom overal in het interne circuit naar de aarde vloeien. Het voornaamste obstakel bij de ontwikkeling van een CDM-robuust

beschermingsontwerp is het gebrek aan kennis over de CDM-stroombron en het ontladingspad door het circuit. Het CDM-overlevingsniveau is erg afhankelijk van het soort behuizing dat voor een IC gebruikt wordt en daarom is het onmogelijk om een circuitontwerp te karakteriseren op CDM-robuustheid zonder het type behuizing mee te nemen in de overwegingen.

In **hoofdstuk twee** wordt de bron van de CDM-stroom geïdentificeerd en een equivalent-circuit-model voorgesteld die een IC gedurende een CDM-stress beschrijft.

Beschermingselementen zijn de essentiële onderdelen van iedere ESD-bescherming. Hoofdstuk drie onderzoekt het gedrag van de traditioneel gebruikte ESD-beschermingselementen bij de zeer snelle stroomtransiënten die bij CDM-optreden. De invoer- en uitvoer- buffers vormen een verbinding tussen de buitenwereld en het hart van het circuit en zijn daarom de meest voorkomende plaatsen voor een CDM-faallocatie. De in de literatuur beschikbare richtlijnen om ESD bescherming te maken beveelt het gebruik van grote weerstanden tussen het beschermingscircuit en het functionele circuit aan. Daarnaast wordt het gebruik van extra beschermingselementen dichterbij het te beschermen circuit aanbevolen. In hoofdstuk vier wordt de invloed van elk van deze ontwerpvariaties en hun gecombineerde effect op de stroom- en spanning-transiënten over de invoer- en uitvoer- buffers bestudeerd.

Het type behuizing speelt een belangrijke rol in de hoogte van het CDM-faalniveau van een element. Als gevolg hiervan dienen CDM-metingen aan hetzelfde circuit herhaald te worden voor elk gebruikte behuizingtype, wat een aanzienlijke hoeveelheid tijd en geld kost. In **hoofdstuk vijf** wordt een methode voorgesteld en geverifieerd om het CDM-overlevingsniveau van een beschermingselement in een bepaald soort behuizing te extrapoleren naar een ander type behuizing. Deze methode vereist een uitgebreide en nauwkeurige karakterisatie van de parasitaire capaciteit en inductie van de behuizing.

Van de diverse oorzaken die kunnen dienen als CDM-stroombron is de capaciteit van de metaalplaat naar geaarde testplaat waarop het circuit gemonteerd is de grootste. De ontladingstroom van deze capaciteit loopt door het substraat via elk mogelijk pad van lage impedantie in het circuitontwerp naar het ontladingspunt. Bij een ontlading van deze substraatcapaciteit kan de spanningsval over het substraat en de circuitelementen, bijvoorbeeld de gate, groot genoeg worden om het falen door CDM te veroorzaken. De kans op CDM-schade veroorzakt door een dergelijke spanningspiek kan niet worden verkregen met de voorheen beschikbare "volledige-chip-modellen". **Hoofdstuk 6** presenteert een nieuw model waarin de substraatcapaciteit en de ontladingsweg

door het substraat en het circuit gedurende de CDM-ontlading daarvan wordt meegenomen.

De toepassing van de voorgestelde methode om het CDM-gedrag te bestuderen wordt beschreven in **hoofdstuk zeven en acht**.

Chapter

### Introduction

The word "electrostatic-discharge", would mean different things to different people. For a nature lover, ESD would bring to his mind the spectacular lightning in the sky, for a school child the magical way by which hair stands while touching the Van de Graaf generator, and for some others, an unpleasant annoying feeling at the tip of one's finger while touching a metallic door knob on a dry weather day. ESD simply put is the "Uncontrolled transfer of static charge between two objects at different potentials".

Though all objects are electrically neutral, rubbing or sliding of one object against another results in charge separation or static charge accumulation. The amount of static charge accumulated on an object depends on its electron affinity and the rate at which the static charge is dissipated into its environment. The presence of static charge creates an electric field extending into space. When an object at different potential is brought close to it, transfer of static charge occurs through the least impedance path available, until both the objects reach the same potential. ESD can be hazardous and life threatening depending on the amount of voltage built up from charge collection and the relative impedance of the discharge current path. For example, a house on which lighting strikes will be completely burnt down from the enormously large magnitude of discharge current flown into the ground through it. But for an event such as lightning to occur, the amount of static charge collection should be very large so as to create a voltage drop as high as 300,000V. It would be surprising to learn that we are exposed to ESD almost every day. And the reason why we do not feel it, is simply because the human body cannot sense any electrostatic voltage drop below 3000V. Therefore ESD becomes our topic of discussion only when the voltage drop associated with ESD exceeds our threshold level (> 3000V).

But ESD has become a major concern for semiconductor industries because the minimum threshold level of its products to ESD stress is very low (much below our sensitivity range). As a result more than 30% of the total number of products returned to the industry because of failure is due to ESD stress. [1, 2]. In this chapter, an overview on the different ways in which the ICs gets exposed to ESD stress, the various test methods available for qualification and characterization of IC products for their ESD robustness and the generally available protection circuit designs is presented.

#### 1.1 ESD in Semiconductor Industry

In the race to miniaturize ICs, device dimensions have gone down rapidly and as result the operational voltage levels and the amount of current carrying capabilities of the circuits have gone down. The discharge current accompanying the ESD stress is much larger than the maximum current which can be safely handled by the circuit without being burnt down. As a result the sensitiveness of ICs to ESD damage has increased with modern technology. In other words ICs have become sensitive to even small charge collection. Most of the ICs face ESD stress when they are packaged and shipped before reaching their customer. Hence the IC producers have to quantify the ESD robustness of their products. This is done through a few test methods that mimic real life ESD events on an IC and the stress level above which the IC gets damaged is evaluated. For the ICs to be stamped as ESD robust, they should be able to withstand a certain minimal threshold level set by any of the international organizations like ESDA, [3]. This threshold level varies with different types of ESD stress. Based on the different ways by which an IC can be exposed to ESD events, four types of models are recognized. They are:

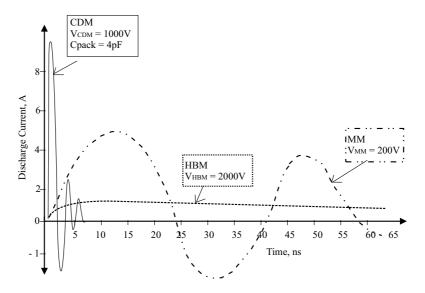

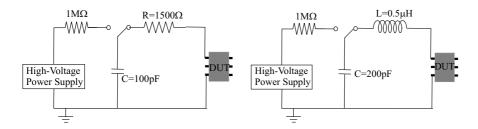

• Human Body Model (HBM): HBM is a model describing an ESD event, encountered by the IC during human handling. It is a two pin event where the charge from the human body flows to the ground though the IC. A HBM stress of 2000V can result in a discharge current of amplitude 1A with rise time of 10ns and a pulse width of 100ns as shown in figure 1.1. The test method used for HBM qualification of ICs is shown in figure 1.2. A charged human body is modelled by a 100pF capacitor pre-charged to its stress level (body capacitance with ground) and a large series resistance of  $1500\Omega$  (body resistance). As per the ESDA standard [4] ICs should withstand a HBM stress level of 2000V to be qualified as HBM robust. The type of failure usually reported on

Figure 1.1: Discharge currents during the HBM, MM and CDM ESD.

the IC from HBM stress, is from excess power dissipation at the I/O protection structures [5]. Hence for ICs to be immune to HBM type ESD stress, protection structures should have a low  $R_{\rm ON}{}^{\rm I}$  such that the power dissipated in the protection device during the ESD event is lesser than the power needed to melt down the silicon.

• Machine Model(MM): MM is a model describing an ESD event encountered when a machine which has static charge touches an IC. A 200V MM stress can generate a discharge current peak of -3.5A with a rise time of 10ns as shown in figure 1.1. The test method used for MM qualification of ICs is shown in figure 1.3. The machines being very good conductors, the impedance offered by it is mainly from its inductance. The capacitance of the machine with the ground is quite large and is modelled by 200pF in the test method. The combination of inductance with large capacitance results in an oscillating discharge current which reaches large amplitudes of current at very low stress levels of even 100V. The ICs are qualified as MM robust, if they could withstand 200V MM stress as per the ESDA standard [6]. The ESD damage on the IC caused from MM ESD stress is similar to that caused from HBM ESD stress, except that the voltage stress level is significantly lower in MM

$<sup>{}^{1}</sup>R_{\text{ON}}$  is the resistance of a device during its conducting (ON) state.

**Figure 1.2:** HBM test set-up.

**Figure 1.3:** MM test set-up.

stress( $\approx 200 \text{V}$ ) as compared to HBM( $\approx 2000 \text{V}$ ).

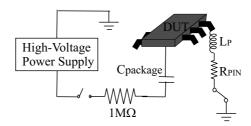

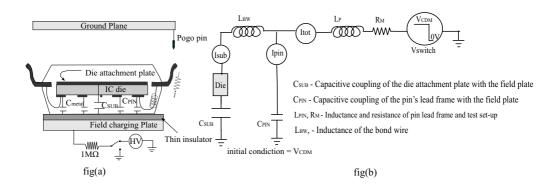

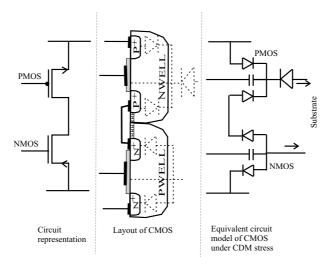

• Charged Device Model (CDM): When a self charged IC touches a grounded plane, Charged Device Model (CDM) type of ESD event is said to occur. During CDM stress, the static charge stored within the IC flows into the outside ground resulting in a large current flow through the circuit. An equivalent circuit model of an IC under CDM stress is shown in figure 1.4. IC being both the source and part of discharge path, the shape of the discharge current is completely determined by both the IC package parasitics and the circuit design. In general the CDM discharge current has very large current amplitude (few ampere) and a very short rise time (fraction of a ns) and is considered as the most severe kind of ESD stress when compared HBM or MM. A comparison of discharge current waveforms from all three types of ESD events is shown in figure 1.1. As per the ESDA/JEDEC standard ICs should withstand a CDM stress level of 1000V to be qualified as CDM robust [7,8]. Different test methods used for CDM qualification are explained in detail in chapter 2. A typical CDM failure signature is the presence of gate-oxide failure distributed within the internal circuits as well [9, 10].

Figure 1.4: CDM test set-up.

• System level ESD: The HBM, MM and CDM events model device level ESD event. A system level ESD refers to the ESD event that an IC can encounter when the working system in which it is mounted, is subjected to ESD stress. (It models the ESD encountered by the IC in its working environment). For example, a system can be a Printed Circuit Board (PCB) on which the IC is mounted. System level ESD then refers to the stress encountered by the IC when the PCB is subjected to ESD stress. The test set-up used to study the robustness of system level ESD stress mimics a charged human holding a metallic object and using the metal tip of the object to contact the frame of a piece of equipment [11]. The system level ESD tester circuit consists of a charging capacitor and a discharging resistor. When an ESD event impinges upon the system, the discharge is indirectly coupled to the operating IC as in a CDM stress event. The effect of system level ESD on an IC is equivalent to subjecting an IC to CDM and HBM stress at the same time. System level ESD is gaining increasing attention in last couple of years as it encompasses both CDM and HBM type of ESD events. But this system level ESD is beyond the scope of this thesis and will not be treated in detail.

#### 1.2 ESD Protection Design

ICs can be protected from ESD damage in two ways.

- Prevention: By avoiding exposure of ICs to static charge by use of air ionizers, use of conducting or antistatic bags and packages for transport and use of grounded wrist straps at the work bench while handling the ICs.

- Self-consistent: By making ESD robust circuit design by implementing on-chip protection.

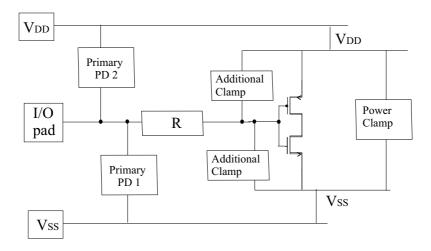

Present industry practice shows that both are necessary to suppress ESD related failures. In this thesis only the second method of ESD protection of ICs is studied. Special protection circuits are built within the IC to avoid the ESD current from flowing into the circuit. Specially designed devices capable of handling large ESD currents and clamping the voltage across the circuit during an ESD event, using a low impedance path are known as Protection Devices (PD). The behavior of these devices will be dealt with in detail in chapter 3. Protection circuits are designed to safely route all the ESD current to the ground through the protection devices, without allowing it to flow

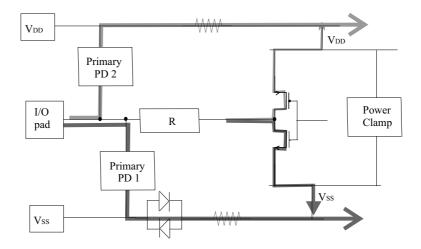

**Figure 1.5:** Pad based ESD protection design.

through the functional core circuitry. Also care should be taken that the built in protection circuits do not hamper the normal operation of the circuit. Two types of protection designs are generally adopted. They are:

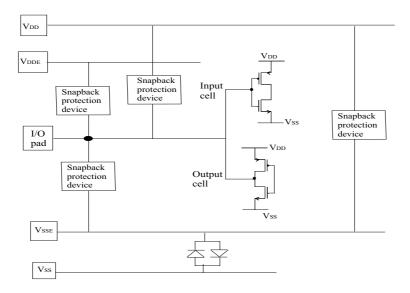

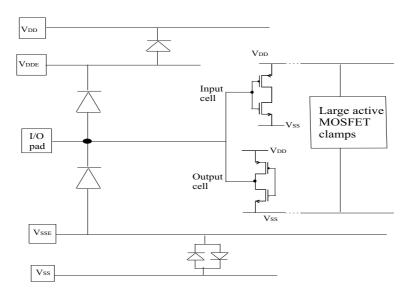

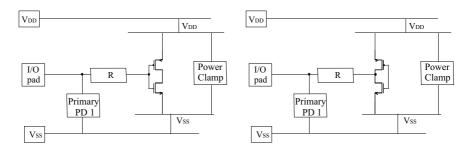

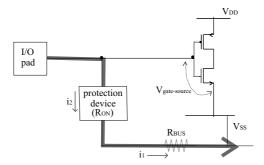

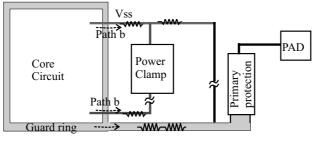

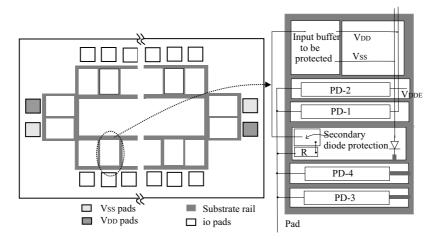

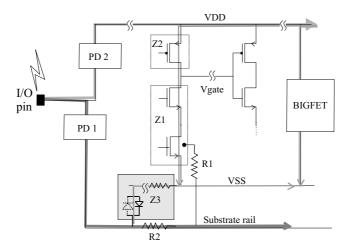

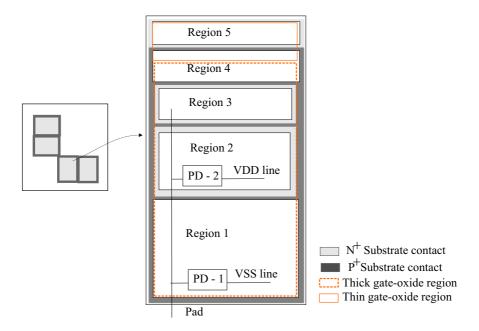

- 1. Pad based protection: A schematic sketch of pad based protection design at the I/O pins is shown in figure 1.5. In this design each I/O pad is clamped to the supply rails by means of one or more protection devices. By this protection design, we make sure that there exists at least one low impedance path through the protection devices, between any two pins during an ESD event. Each V<sub>DD</sub> pad has a clamping device to the ground line of the circuit but are not connected to other V<sub>DD</sub> rails. All the protection devices used in this design are typically snapback devices which act more or less as an open under normal operational conditions and as short during ESD stress [12]. The device parameters of the snapback devices changes from one technology node to another. As a result, pad based protection design from one technology node cannot be directly used in another without being optimized.

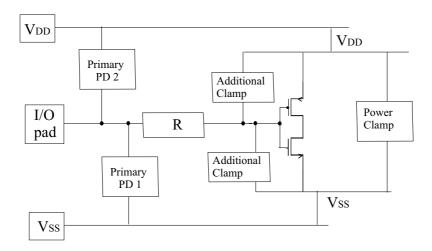

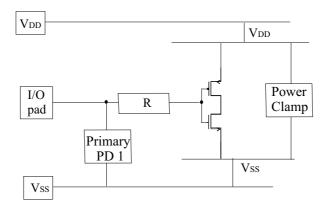

- 2. **Rail based protection:** In rail based protection, the supply rails are clamped with each other through a single or series of diodes in its reverse biased mode under normal operational conditions or through an large

**Figure 1.6:** Rail based protection design.

active Metal-Oxide-Semiconductor Field-Effect-Transistors (MOSFET) or a large Nwell capacitor. Each I/O pad is clamped to the supply rails by a diode in its reverse biased mode under normal operational conditions. In mixed signal circuits, the different  $V_{\rm DD}$  rails are also clamped to each other through diodes as shown in the figure 1.6. This avoids any kind of voltage overshoot across the supply rails to exceed beyond a critical voltage level, during its normal operational conditions as well [13]. The device parameters of protection devices used in a rail based protection design mainly diodes, do not change with different technologies. As a result, rail based protection design more preferred as they can be easily transferred from one technology node to another.

#### 1.3 ESD Characterization Methods

The HBM, MM and CDM test methods used for ESD qualification gives the maximum withstand level of the IC but does not help in studying the device behavior during ESD stress. Study of the device behavior during ESD stress is very crucial for optimizing the device layout parameters to achieve maximum ESD robustness. In this section, two types of characterization methods used to

**Figure 1.7:** TLP test set-up.

study the high current transient behavior of protection structures under HBM like or CDM like ESD stress is explained.

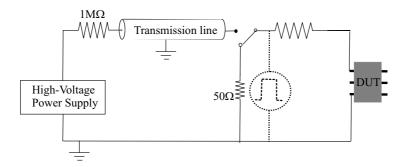

#### 1.3.1 Transmission Line Pulse

Tim Maloney, in the year 1985 [14], suggested the use of Transmission Line Pulse (TLP) in order to characterize the protection circuits during an ESD event. The basic principle TLP consists of charging a  $50\Omega$  coaxial cable through a high voltage supply, and then discharging it through a  $50\Omega$  resistor as shown in figure 1.7. The resulting waveform is a rectangular voltage pulse, whose pulse width is directly proportional to the length of the transmission line cable and amplitude half of the pre-charged level. Roughly a transmission line of length 1m translates to a voltage pulse of pulse width 10ns. This rectangular voltage pulse is passed through a high resistance R, resulting in a rectangular current pulse. During TLP measurement, this constant current pulse  $I_{DUT}$  is driven into the Device Under Test (DUT) and the voltage drop across it  $V_{\text{DUT}}$ is observed through the oscilloscope. Thus the transient behavior of the device under a given stress level is studied. This process is repeated for higher current amplitudes in specified step size, until the device finally breaks down. The device failure level is studied by performing leakage current measurements under normal operational conditions after each stress level. Thus the high current current and voltage characteristics of the device under high current transients can be extracted from these measurements. A 100ns TLP current source with an impedance of approximately 1 k $\Omega$  is used to emulate HBM conditions. It has been shown by several authors [15–19] that the failure threshold level of a circuit from TLP measurements can be correlated to its failure level under HBM and MM stress measurements. Thus it is not surprising that TLP is be-

**Figure 1.8:** vfTLP test set-up.

ing used extensively to both characterize and qualify their IC chips for HBM and MM immunity, by ESD engineers all over the world.

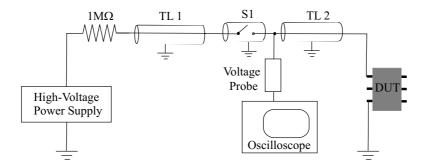

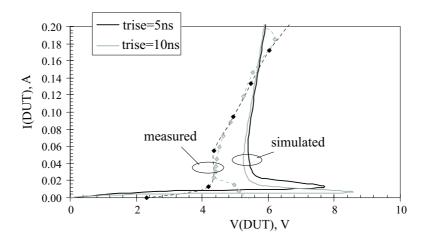

#### 1.3.2 Very fast Transmission Line Pulse

In order to emulate high-current conditions similar to CDM, a large current pulse of rise time closer to CDM rise time is used. Such fast transient (2ns to 3ns) are known as very fast TLP (vfTLP). Realization of a TLP with a very fast current rise time, short pulse duration and high amplitude with the set-up described in section 1.3.1 is very difficult. Hence vf-TLP system was designed as a high-current time domain reflectometer by Horst Gieser [20]. In this system, an incident voltage pulse of short duration defined by the length of TL1 travels from pulse generator to the DUT via TL1 and S1 and is reflected at DUT. The voltage of the incident and the reflected pulses are measured with a voltage probe between S1 and TL2. TL2 is made sufficiently long so as to avoid the overlap of the incident and reflected pulse. In order to obtain  $V_{\rm DUT}$  and  $I_{\rm DUT}$ , a single waveform record containing incident and reflected pulse is spilt up and the reflected pulse is superimposed on the incident pulse. Attempts are made to characterize device behavior under CDM stress using vf-TLP measurements [21]. But one should not forget that this extrapolation is perfectly agreeable only if the current path is the same in both the cases. CDM stress being a one-pin event, the discharge current path is not exactly the same as in vf-TLP which is basically across any two pins in an IC. Hence the application of vf-TLP stress to study the device behavior under CDM stress is still under debate.

#### 1.4 Scope of this Thesis

With the present modern and future technologies, the threat to ICs from CDM type of ESD stress has increased. This is because increased usage of automated handlers have made the ICs prone to more frequent CDM type of ESD stress. Decreased device dimensions, especially thinning down of gate-oxide thickness has made ICs more vulnerable to CDM damage. Hence it is mandatory to study the various means of protecting the ICs from CDM damage.

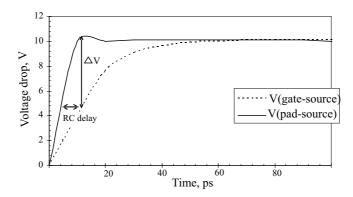

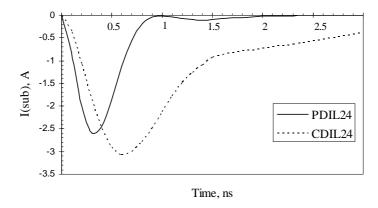

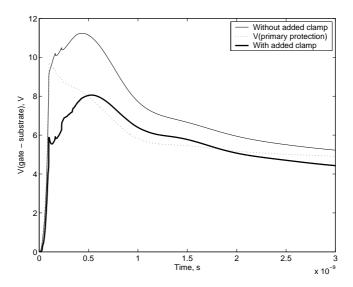

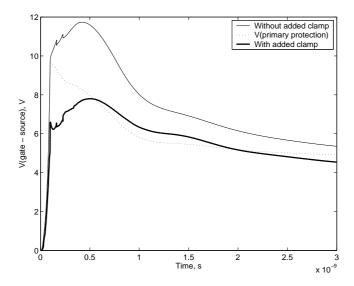

The large amplitude and very short rise time of CDM discharge current poses two additional requirements on the protection design. First, large current flow through the small bus line resistance of the metal lines in the circuit can cause significant amount of voltage drop across it adding to the voltage over the protection device. Hence the parasitic bus line resistance has to be taken into consideration as well. Secondly, the protection devices should have turn-on time  $t_{\rm on}^2$  faster than the rise time of the CDM pulse. If not the voltage across the circuit will not be clamped and the large voltage overshoot across the MOSt gates will result in gate-oxide failure [22,23].

In the case of CDM stress, the IC itself is the source. When any one of the IC pin touches a grounded plane, charge from within the IC, flows into the ground through any low impedance path available in the circuitry. Thus there is no specific discharge path for the CDM current. The protection designs presently used are restricted to the input and output (I/O) cell regions and hence are well suited for any two pin ESD event where the ESD current flows from one pin to another. But with the CDM discharge current being distributed throughout the circuit, there is a need to have a distributed protection design [9, 24]. Also CDM robustness of given circuit design varies from one package to another [25,26]. There is no clear border between the influence of the package and the circuit design on the CDM performance of a circuit.

vf-TLP measurements can help in studying the high current transient behavior of the individual protection devices. But their replacement to study the behavior of protection device under CDM stress is under question.

CDM measurements gives "pass" or "fail" results and does not provide any insight into the behavior of the circuit under CDM ESD event. Any attempt made to study the current or voltage transients within the internal nodes during CDM stress, results in large intervention on its path through the circuit and thus do not provide any reliable information. On the other hand, circuit sim-

$<sup>^{2}</sup>t_{on}$  is the time taken to change from high impedance OFF state to low impedance ON state.

ulations not only help in evaluating the IC performance but can also be used to access the current and voltage transients at any internal nodes under CDM stress without intervening its circuit behavior. Thus simulations can help in analyzing the CDM behavior and hence in faster optimization of the circuit design.

#### 1.5 Thesis Outline

We know that CDM damage is caused from charge transfer by the IC to a grounded pin. But the answers to basic questions such as "Where is the charge stored? What is the path of charge transfer? What role does the package parasitics play in determining the CDM failure level of an IC? What are the exact IC parameters that influence the CDM performance of an IC?" are not very clear. This thesis attempts to answer the above listed questions. It investigates the various elements of an IC that can influence its CDM behavior, and provides a suitable circuit model of the entire IC under a CDM test set-up. The model is applied to predict the weak locations in the circuit vulnerable to CDM damage. General protection design issues that needs to be considered for designing a CDM robust IC is presented.

In chapter 2, the dynamics of static charge flow through the circuit during a CDM stress in real-life and the closeness of the various test methods used for CDM quantification, to a real-life event is studied. The pros and cons of experimental measurements and simulation studies on circuit behavior under CDM stress are listed. An overview of the circuit models presently used for CDM simulations to study the CDM behavior of an IC and their incompleteness/limitations is presented. The need for a full chip CDM model and various IC properties that needs to be taken into account when developing a full chip circuit model is emphasized. An equivalent circuit that can completely represent an IC under Field induced CDM test set-up is presented in a lumped circuit model.

Protection Devices are one of the most important parts of the protection design. These are the specially designed devices that clamp the voltage across the circuit, by providing a low impedance path during an ESD stress event. In chapter 3, CDM and TLP performance of protection devices with varying layout parameters are studied. The compact circuit model used in our simulations to model the device behavior under CDM stress is explained. The high current transient behavior of the device from simulations is cross checked with TLP and vf-TLP measurements.

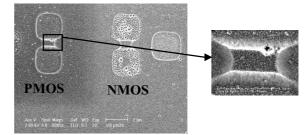

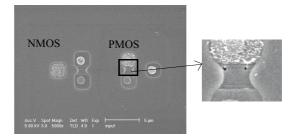

I/O protection circuits are one of the most vulnerable locations to gate-oxide failure as the corresponding gate (input) or drain (output) is in direct contact with the discharged pin. In chapter 4, the CDM performance of I/O protection circuits with varying designs is studied. The role of each design parameter on the CDM robustness of the circuit is extracted.

The amount of charge stored within an IC depends on the package type and the failure location depends on the discharge current path through the circuit. Hence there is no clear distinction on the effects of package and circuit design separately on the CDM performance of an IC. As a result, even if the circuit design is the same, CDM measurements have to be repeated each time the package type is changed. In chapter 5, the role of package parasitics and a suitable method for the CDM threshold level of a circuit design in one package to be extrapolated to other packages is investigated. The proposed method is applied to identical test structures in different packages and its correctness verified.

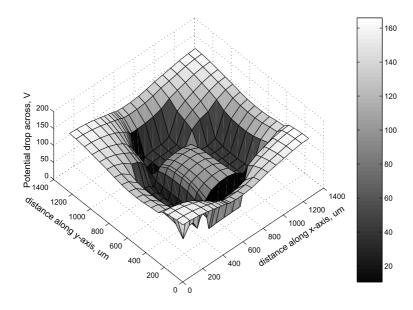

The main source of CDM current is from the capacitance formed by the die attachment plate on which the IC chip is mounted. The discharge path of this capacitor into the grounded pin is through the circuit elements present on the substrate. Thus substrate resistance plays a very crucial role on the CDM performance of the IC. In chapter 6, a suitable method of modelling the substrate capacitance and its discharge path through the various devices in the circuit design during CDM ESD is presented. The effect of substrate resistivity variation on the voltage transients seen across the silicon under CDM stress is studied. The limitations on the circuit model are also presented.

The full chip circuit model is applied to study the CDM behavior of two test circuit designs. The first test circuit has pad based protection design and the second has rail based protection. The effect of substrate contact distributions on the voltage transients across the gate-oxide of the MOSt in the circuit designs are studied in chapter 7 and chapter 8.

# 2 Chapter

## IC under CDM Stress

The question on where the static charge is stored and how the charge transfer take place during CDM type of ESD event is still unanswered. In this chapter, the dynamics of CDM current in real-life CDM event and in the test methods used to quantify CDM robustness are studied. An equivalent circuit that can be used to simulate the same transients in the circuit as in one of the test methods namely field induced CDM test set-up is developed.

#### 2.1 Introduction

The danger of IC failure from the discharge of static charge on the IC was first reported by Speakman [27]. Soon it was discovered that CDM type of failure was reported to occur more frequently and the need for CDM protection has become an absolute requirement for all IC products. In order to protect a circuit against ESD damage, one should know its discharge current path through the circuit during ESD stress. For CDM ESD protection, this means one should know the static charge source and its path through the circuit, when one of its pins touches a grounded surface. Any test method or simulation employed/used to study the CDM performance of an IC should cause the CDM current to flow in the same path as it occurs in the real-life CDM ESD event.

The basic understanding on how ICs are charged and how the charge transfer causes damage to an IC in a real-life CDM event is reviewed in this chapter. The various test methods used for CDM quantification, and their resemblance to real-life CDM event is studied. The limitations of CDM measurements and advantages of circuit simulation study over actual measurements are analyzed.

The need for full chip CDM model and the various IC elements that it needs to take into account in developing a CDM circuit model is investigated. An overview of the circuit models presently used to study the CDM behavior of an IC is presented and their incompleteness in modelling the CDM behavior is studied. An equivalent circuit that best represents an IC under field induced CDM test set-up is developed.

#### 2.2 CDM in real-life

When two objects of dissimilar materials collide or rub against each other, transfer of electrons from one to another can occur resulting in static charge creation. This process of electrostatic charge creation is known as triboelectric charging. In the production environment, ICs face triboelectric charging in several ways:

- Usage of tape and reel packaging materials

- Usage of adhesive tapes during assembling

- Rubbing or sliding of IC against the surface of a bag or a tube while shipping

- Usage of device marking equipments which put static charges on the packages of the ICs

Thus we see that charge is accumulated on the package material or on the metal leads of the IC during the various stages of IC processing. Static charge on an insulating surface remains on the surface without moving or spreading out, whereas the static charge collected on a conducting surface spreads out to avoid charge imbalance on its surface. In other words, the charge decay time of conductors is shorter than insulating materials. Therefore it is not unappropriate to assume that the static charge responsible for CDM ESD resides on the insulating package material of the IC. No matter where the charge is present, our concern is how this charge affect the CDM performance of an IC. The charge on the IC package is capacitively coupled to the conducting layers of the IC as shown in figure 2.1. From Gauss' law we know that as charge Q approaches a grounded surface its potential with respect to the grounded surface increases. The gradient of the electric field arising from the presence of charge is given by,

$$\nabla . E = Q/\varepsilon \tag{2.1}$$

Figure 2.1: CDM in real-life.

where,  $\varepsilon$  is the permittivity of space. The relative potential of the IC with respect to the ground, just before it touches the grounded plane is given by,

$$V = Q/C (2.2)$$

where,

Q - Charge stored in the IC package,

C - Net capacitive coupling between the conducting layers of the IC and the ground.

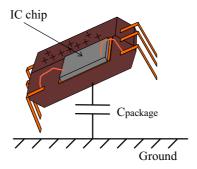

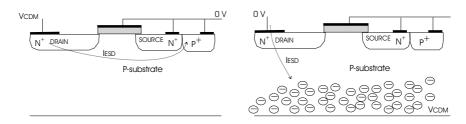

When one of the IC pin touches a grounded surface, there is a sudden drop in the potential across the IC, causing charge to flow from the IC to the ground. The amount of charge that flows through the circuit depends on the potential of the IC before it touches the ground and the package capacitance that discharges through the circuit. It is not the presence of static charge itself, but the flow of charge arising from the potential drop developed as a result of charge collection which causes the ESD damage. This is also the reason why some ICs without any static charge but placed in an electrostatic field (or equivalently at different potential) have been reported to have CDM damage.

ESD current arising from CDM stress can be considered as the discharge current of the IC capacitor  $C_{\rm package}$ . If we closely examine  $C_{\rm package}$ , it is not a single capacitor, but a composite of several capacitors formed by the various conducting layers in the IC with the ground and package as its dielectric. When a particular pin touches a grounded surface, all these capacitors discharge through their connections to the grounded pin. The extent to which each of these capacitors influence the CDM performance of an IC depends on its relative magnitude and its discharge current path to the grounded pin

through the circuit.

#### 2.3 Failure encountered from CDM Stress

Discharge current flow through an IC during CDM stress causes two types of failure.

1) Thermal Failure: One does not expect failure from excess heat dissipation to occur from CDM stress as the stress time is very short [28]. This is also one reason why we cannot make a direct extrapolation of the CDM failure level of a protection device to its failure level under vfTLP stress. Nevertheless thermal failures do occur from CDM stress if there is non-uniform conduction of ESD current through the protection device [1,29]. This type of failure can be considered as a direct consequence of CDM current flow.

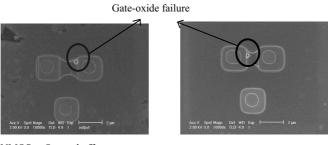

**2)Gate-Oxide failure:** CDM current flow through the circuit, causes the potential drop seen by the gate-oxides of the MOSt to sometimes exceed its oxide breakdown voltage resulting in gate-oxide damage. This is yet another reason why ICs have become more vulnerable to CDM failure especially with the thinning down of gate-oxide thickness. This indirect effect of the CDM current is most often referred to as "the CDM failure" [30].

#### 2.4 CDM Test Methods

The aim of the test methods are to reproduce the same effect on the IC as it occurs during a real-life CDM event and to help in evaluating the IC's robustness against CDM stress. The amount of charge stored and discharge current path through the circuit should be the same in the test method as in real-life CDM event. Hence the parasitic elements in the test set-up should be kept small such that the amount of charge stored and the discharge current flowing through the circuit is greatly determined only by the IC and not the tester parasitics. A lot of research has been done in developing a test method to duplicate real life CDM events starting from 1980s [31,32].

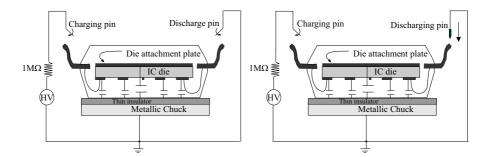

#### 2.4.1 Non-Socketed Test Method/CDM

Non-socketed test method was the first test method introduced to simulate CDM stress event. It is also known as the robotic test method. In this test

**Figure 2.2:** Direct contact mode.

**Figure 2.3:** Direct non-contact mode.

method, the IC is placed on a metallic plate with its pins facing up (dead bug position). Based on the charging method it can be subdivided into two types, namely,

- 1. Direct charge method: Direct charge method was introduced by Bossard [33] and later developed by others [34]. This method mimics a CDM event which occurs when the IC pin gets charged by triboelectricity. The IC is placed on a grounded plate as shown in figure 2.2 and figure 2.3. The IC is charged either through the pin which provides the best ohmic connection to the substrate or through all the pins simultaneously [7, 8]. The charging process is done slowly so that no damage is encountered during this process and the potential of the entire IC is raised to the electrode's potential. The discharge is initiated by sudden grounding of the pin corresponding to the circuit or device to be tested. The discharge can be done in two modes, the contact mode or the non-contact mode. In contact mode discharge is initiated by an arc within a relay. The relay is metallically connected to the component pin via a socket or probe. And in the non-contact mode, discharge is initiated by an arc between a probe tip and component tip. The main disadvantage is the risk of destroying the IC during the charging up process rather than during discharge.

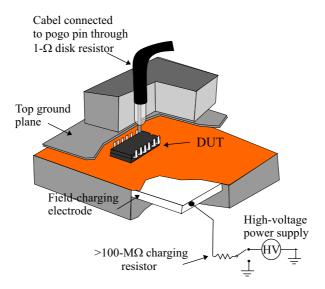

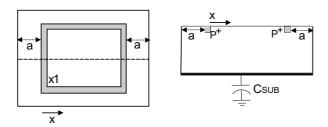

- 2. **Field charge method (FCDM):** Field induced charged device model was introduced by Renninger [35]. This is the most commonly used test method for CDM qualification of IC products. This method mimics the CDM event which occurs when the package material of the IC gets charged or when an IC at different potential is subjected to CDM stress. The test set-up for a FCDM test method is shown in figure 2.2. It consists of a metallic plate known as field plate connected to a high voltage supply. By placing the IC on this field plate, the potential of the entire

Figure 2.4: FCDM tester set-up.

IC is raised to that of the high voltage supply connected to it. The size of the plate is at least seven times larger in area than the size of the IC to be tested. This is done to ensure that the IC is subjected to uniform electric field and to ensure that there is no potential difference within the IC during the charging up process. The various capacitors within the IC are as shown in figure 2.2. The field-charging plate of the test set-up forms one electrode of the capacitor, the package material and the thin dielectric sheet (used for avoiding charge leakage) represents the dielectric of the capacitors and the various conducting layers in the IC forms the second electrode of the capacitors. Prior to discharge, the field electrode will be at ground and the second electrode (silicon die and the lead frame) will be at the pre-charged potential. Discharge occurs either by contact method or non-contact method where the discharge probe connected to a grounded plane touches or comes close enough to cause ESD of the pin to be CDM stressed. This initiates the discharge of the various IC capacitors through their connections to the grounded pin. Thus the amount of charge stored and the discharge path is greatly determined only by the IC parasitics. The discharge probe is kept small to keep the influence of tester parasitics on the shape of the discharge current minimal. Although the non-socketed test methods mimics a real-life CDM event very well, they have the disadvantage of being very laborious, consuming a large amount of time. Moreover for ICs with large pin counts and small pitch size (small spacing between adjacent pins), discharge of individual pins cannot be guaranteed by this test method.

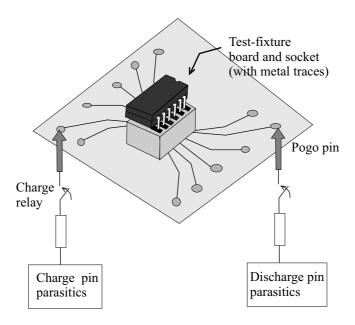

#### 2.4.2 Socketed Test Method

The Socketed Test method was introduced to increase the IC manufacturer's CDM testing throughput. This technique has been in progress since 1990 [36]. In this test method the IC is placed in a socket with its pins facing down (live bug position) as shown in figure 2.5. The socket is then charged by a high voltage supply. Discharge is initiated by sudden grounding of the respective pin. By making suitable sockets, individual pins of an IC can be easily addressed even with small pitch size. But the main disadvantage of this test method is that the amount of static charge stored is largely decided by the test set-up parasitics rather than the IC parasitics [25, 37–39]. Hence Socket Test results were found to be independent of the package parasitics whereas in real-life CDM, we observe a strong dependency of CDM robustness on the package type. Because of the large intervention of the parasitics in the test set-up on the CDM test results, the usage of this test method is now restricted to identify the weak products and is not used for product qualification.

#### 2.5 Need for CDM Simulation

The test methods available for CDM quantification help us to know the maximum withstand level of an IC product but does not tell why the circuit design had failed. The post diagnosis of the failure location requires extensive and careful de-processing of the entire circuit design and not the protection device at the I/O region alone. Redesigning of the circuit is done on a trial and error basis which consumes immense amount of time. To design an efficient protection circuit design, it is just not sufficient to know its CDM robustness level alone. Equally important is to know why a protection design is robust or why not. In other words, it is necessary to study the behavior of the circuit under CDM-ESD event. Any attempt made to measure the current or voltage transients within the internal nodes during CDM stress, results in large intervention on the shape of the ESD current and its path through the circuit and thus does not provide any useful information.

On the other hand, simulations help to access the internal circuit nodes without intervening the device or circuit behavior under CDM stress. Study of

**Figure 2.5:** FCDM tester set-up.

circuit performance based on simulations gives much faster feedback on the efficiency of the protection circuit design than the time taken in actual production of test samples, testing their CDM performance and evaluating their failure locations. If the CDM circuit model used in the simulations is made as accurate as possible, it can help in designing/redesigning an efficient protection circuit within one or two production cycles and can thus save large amount of time and money.

## 2.5.1 Requirements for CDM Circuit Model

To protect a circuit from ESD damage, one should know the source of the ESD current and its discharge path through the circuit. For CDM-ESD, the current sources are the various pre-charged capacitors in the IC and the discharge path is the discharge current path of these capacitors to the grounded pin. The circuit model used to evaluate CDM performance of an IC should therefore model the IC capacitors and the circuit elements through which they discharge. For a concise prediction of CDM discharge path in a chip, "Full-Chip Circuit Model is a MUST for CDM Simulation Studies".

Figure 2.6: Lumped model for chip under direct charge test method by Jaesik Lee.

#### 2.6 CDM circuit simulation - State-of-the-art

Simulations can be classified in two categories, namely device level and circuit level. Device level simulations are focussed on modelling the behavior of devices especially protection devices under high current transients such as CDM-ESD current by using device simulations or compact circuit models [25,40–42]. Circuit level simulations are used to evaluate the efficiency of I/O protection design under CDM like ESD stress [43,44]. These simulation studies has helped us to a large extent in understanding and modelling the behavior of protection devices and circuits under fast current transients. But they cannot be applied to evaluate the CDM performance of the entire IC. This is simply because the CDM discharge current is not restricted to the I/O regions, but can be through any low impedance path through the circuit. Moreover these simulation methods do not model the one pin stress condition and the distributed nature of CDM discharge current.

## 2.6.1 Previous Chip Level Circuit Model

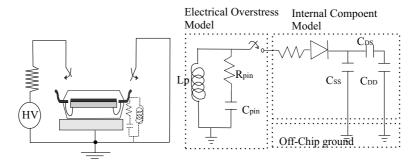

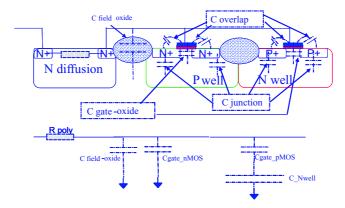

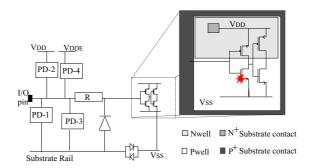

A chip-level simulation methodology for CDM was presented by Jaesik Lee [24]. The model is used to study the transfer of charge from the internal conductors in the circuit design to the grounded pin during a direct charge test method. The entire circuit design is partitioned into subsystems and each subsystem is modelled by an equivalent circuit known as macro model and a full set of such macro models represents the CDM behavior of a whole system. The equivalent circuit of the small subdivisions used to build the entire circuit design is shown in figure 2.6. The CDM current source is modelled by  $C_{\rm DD}$  and

$C_{\rm SS}$  which represent the capacitance between  $V_{\rm DD}$  and  $V_{\rm SS}$  conductive planes and the off-chip system ground, respectively. The capacitance  $C_{\rm DS}$ , represents all the capacitance between the on-chip  $V_{\rm DD}$  and  $V_{\rm SS}$  planes including junction capacitance, oxide capacitance, direct metal-to-metal coupling capacitance, Nwell-to-p-substrate capacitance and decoupling capacitance. When any pin is grounded, rapid charge transfer takes place from  $C_{\rm SS}$  and  $C_{\rm DD}$  to the grounded contact resulting in a large current flow through the internal components. A large voltage overshoot across  $C_{\rm DS}$  during CDM stress simulation indicates the possible location of CDM failure. The circuit model takes into account the distributed nature of the CDM current source and the bus line resistance of the power lines. Also it captures the one pin nature of the CDM stress. The CDM performance of a circuit design is evaluated by studying the voltage drop across the gate and source nodes of MOSts during a CDM stress.

#### Limitations of the model

The CDM current sources are the several pre-charged capacitors of an IC as explained in section 2.2. The contribution of each of these capacitors to the CDM performance of an IC depends on its magnitude and its current path through the circuit. In this respect, the capacitance formed by the die attachment plate, with the system ground or field plate, the substrate capacitance  $C_{\text{SUB}}$  plays a significant role [45]. This is because of its large magnitude when compared to other capacitors and its discharge path being distributed throughout the entire circuit through the common substrate. Hence a major portion of the discharge current is from the substrate to the discharged pin through any low impedance path available in the circuit design. Grounding of a pin does not only cause voltage drop across the internal nodes of the circuit design but also across the substrate and circuit elements. The voltage drop across the substrate and gate can also result in gate-oxide damage. In the CDM circuit model presented by Lee, the CDM current source is modelled by the power line capacitors  $C_{\rm DD}$ and  $C_{\rm SS}$  alone. It does not take into account substrate capacitance  $C_{\rm SUB}$  and its discharge path through the substrate.

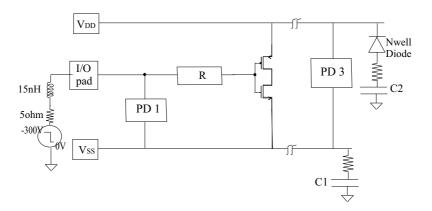

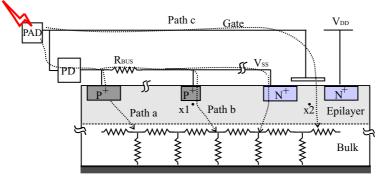

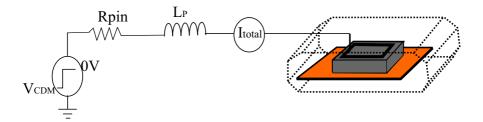

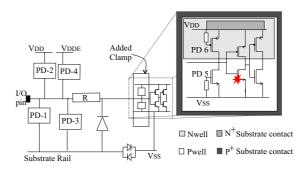

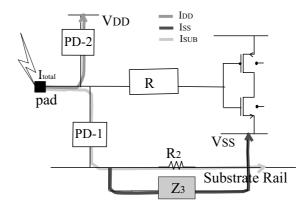

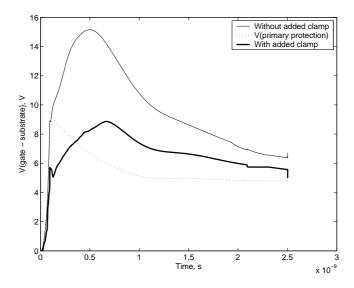

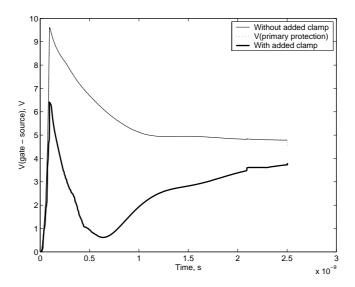

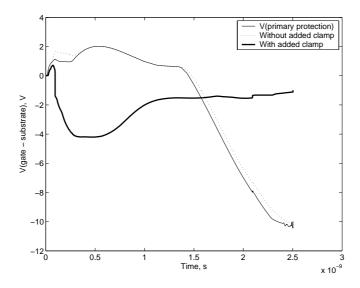

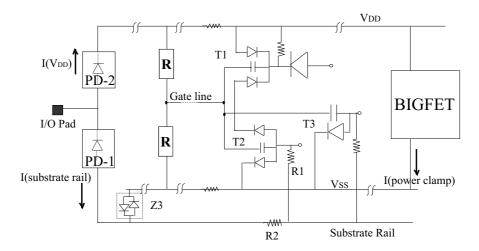

## 2.6.2 Proposed CDM Model

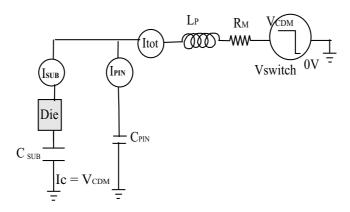

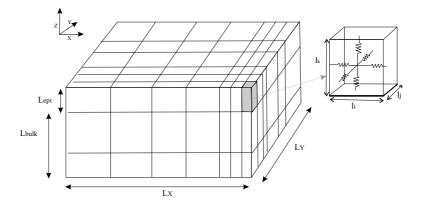

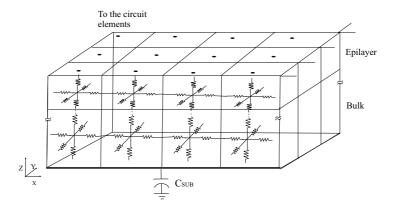

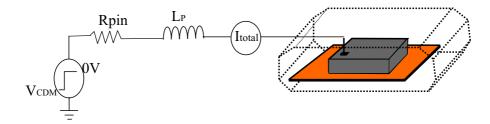

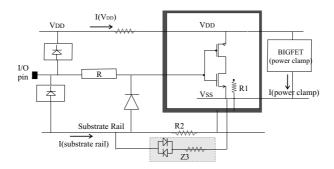

An IC under FCDM test and its equivalent circuit model is shown in figure 2.7. To make the model less complex, we have neglected the discharge current contribution from capacitance associated with the circuit design, i.e. the capacitance of the metallization lines in the circuit with the field plate is neglected.

Figure 2.7: Lumped circuit model for a chip under FCDM test method.

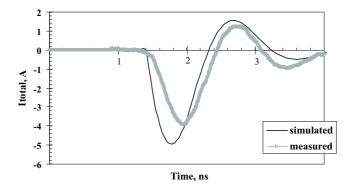

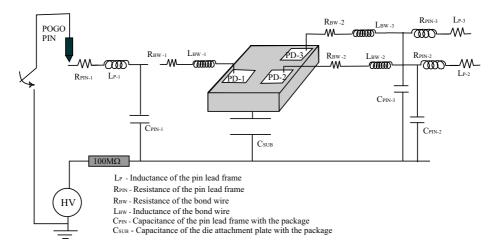

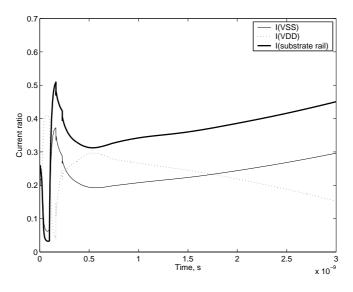

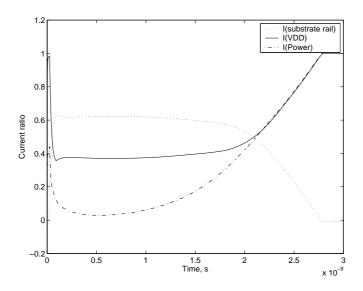

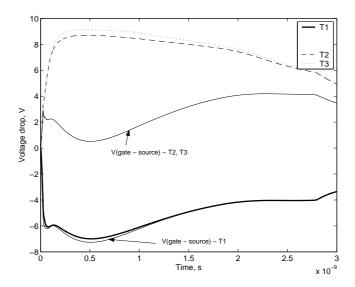

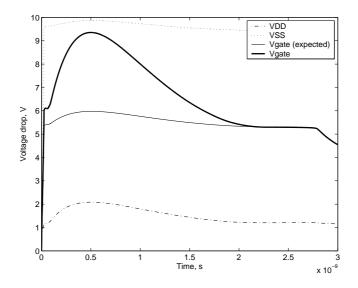

This approximation can be justified because of their relatively small contribution to the discharge current when compared to  $C_{SUB}$ . The CDM current source is modelled by capacitors  $C_{SUB}$  and  $C_{PIN}$  which are pre-charged to the CDM stress level say  $V_{\text{CDM}}$  V. Grounding of the discharged pin is modelled by the sudden drop in the potential of  $V_{\text{SWITCH}}$  from  $V_{\text{CDM}}$  to 0V at time t=0 s in the circuit as shown in figure 2.7. In this way, the one pin nature of CDM stress is taken care of. To know the correctness of the simulation model, the discharge current waveform from simulation is compared to the measured discharge current when a complete circuit in a 80 pin QUAD package was subjected to -250V CDM test. The circuit is replaced by a resistor R in the simulation. The package parasitics  $C_{SUB}$  and  $C_{PIN}$  were measured using a C-V meter at  $1 \mathrm{MHz}$  frequency at  $30 \mathrm{mV}$  and  $L_{\mathrm{P}}$ , the inductance of the pin is taken as the summation of the pin inductance (from RLC measurements of the package) and that of the pogo pin of the tester. The value of resistor R which matches closer to the measured discharge current was chosen to replace the die and circuit. Figure 2.8 shows that the simulated and measured CDM discharge current waveform agrees to a reasonable degree of accuracy. The discrepancies in the simulated and observed results can be attributed partly due to the elementary lumped model of the die used in the simulation and partly to the additional parasitic values from the CDM tester used for measuring. Note that the total discharge current is the sum of the discharge currents from  $C_{PIN}$  and  $C_{SUB}$ . However, only the current from the latter is of significance as it represents the actual current that flows through the circuit and causes CDM damage in the IC. The equivalent circuit model shown in figure 2.7 is partly incomplete because the silicon die along with the circuit is lumped into one resistor. To be able to use this circuit model to study the CDM performance of a given circuit design,

**Figure 2.8:** Measured and simulated total discharge current of an IC in a QUAD 80 pin package.

Figure 2.9: Overview on composition and content of this work.

the resistor representing the circuit has to be further expanded to include the distributed nature of the discharge current through the circuit. In other words, the silicon die along with the substrate and the circuit elements and protection devices should be replaced by their equivalent CDM circuit models instead of a lumped resistor. detailed the need for a full chip circuit model to study the CDM performance of an IC, the rest of the chapters are organized as shown in the flow-chart 2.9, to address the various aspects of an IC that needs to be modelled and their role in determining the IC's CDM performance.

#### 2.7 Conclusions

In this chapter, the basic phenomenon of charge transfer during CDM-ESD event is studied. The limitations of experimental measurements in evaluating the CDM performance of an IC and the need for circuit simulations is emphasized. A full chip lumped circuit that models the transfer through and IC during CDM stress event is proposed.

# **?** Chapter

## **Protection Devices**

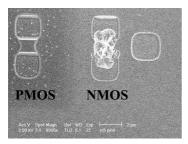

The aim of a protection circuit is to route the electrostatic discharge (ESD) current safely into the ground through some special devices in the circuit, capable of handling large currents. The properties of these devices which make them suitable candidates for ESD protection is outlined and the special requirements on these devices for CDM protection is briefed. Influence of layout parameters on the CDM robustness level are studied for few commonly used protection devices like grounded gate MOS transistor (ggMOS) and low voltage triggered SCR transistor (LVTSCR) from experimental measurements. Further, a compact circuit model for MOS which can simulate its high current transient behavior during CDM stress is presented.

## 3.1 Introduction

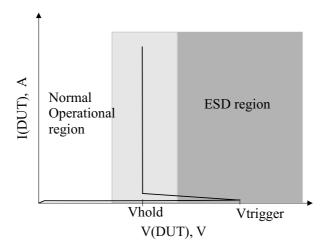

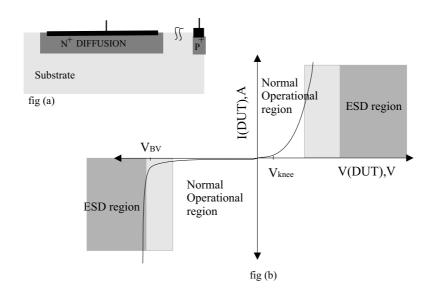

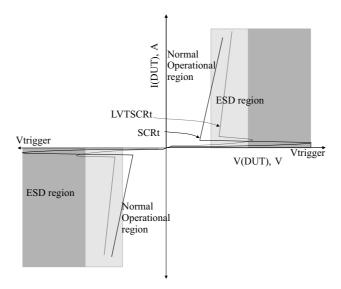

To protect the ICs from ESD damage, special protection circuits are built-in into the IC design. The aim of the protection circuit is to route the ESD current safely to the nearest ground, without damaging the circuit. These protection circuits consist of special devices known as protection devices. Ideally speaking protection devices act as an open under normal operational conditions, drawing zero current through it and as short under ESD conditions, drawing all the ESD current through it into the ground. Figure 3.1 shows the ideal *I-V* characteristics of a protection device. ESD currents from CDM stress reach large amplitudes (few ampere) in a very short rise time (fraction of a ns). This fast transient characteristic of CDM discharge current places an additional requirement on the protection device to have a turn-on time shorter than the rise

**Figure 3.1:** *I-V* curve of an ideal protection device.

time of the CDM pulse. In this chapter, the high current transient behavior of some of the most commonly used protection devices and the influence of their layout parameters on its CDM threshold/failure levels is studied. An efficient compact transistor model for MOSt's under CDM stress is developed in the SPECTRE simulator environment and the simulated high current transient behavior compared with TLP and vf-TLP measurements.

## 3.2 Device physics

Protection devices form the core of a ESD Protection circuit. To design devices that can handle large ESD currents, it is important to study their device behavior under such large current transients. The physics behind the operation of some of the most commonly used protection devices is elaborated in this section.

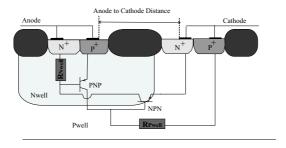

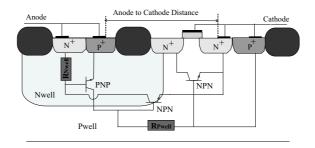

#### **3.2.1 Diodes**

Diodes are the most simple of all devices and are one of the most commonly used protection device. The *I-V* characteristic of a diode and its design layout on a circuit are shown in fig(a) and fig(b) of figure 3.2. One end of the diode is connected to the circuit while the other end is the actual substrate.

**Figure 3.2:** fig(a) - layout of the diode and fig(b) - *I-V* characteristic of a diode under different regions of operation.

The substrate connects to the ground line through the substrate contacts. Under CDM like stress, where the current path is mainly from the substrate to the discharged pin, diode can be considered as a one pin device. The series substrate resistance between the diode and the substrate contact will not be in the CDM discharge current path and hence one may expect a better CDM performance of the diodes as compared to diodes subjected to other ESD stress. This can be true only if the substrate at the diode location is well connected to the ground or supply lines which are connected to the I/O pins. In their forward biased mode, they act as high conducting devices providing low impedance. This is the most preferred state for ESD current. In the reverse biased mode, they do not conduct current until the junction reaches its breakdown voltage. Beyond breakdown voltage, it becomes highly conducting. But as the current conduction through the device is from an avalanche breakdown junction, the diode is in a very unstable state and the devices can easily burn down when operated in this region during the entire duration of the ESD stress. Diodes in the protection circuit are built in such a way that during the normal operation of the IC, these devices are in reverse biased state and are in forward biased state in the worst case scenario of ESD stress.

**Figure 3.3:** Layout of ggNMOSt.

#### 3.2.2 ggMOSt

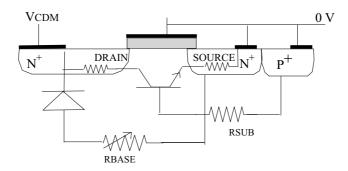

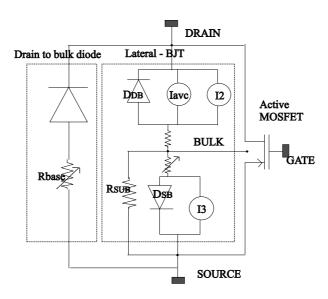

A MOSt, whose gate node is shorted to its source node is the most commonly used protection device in CMOS technology. Under normal operational conditions this device offers very high impedance and thus acts as an open. Under high current conditions, it is not the MOSt which turns on but the parasitic device present in the MOSt that turns on providing a very low impedance path. This property of the device is utilized for ESD protection. The device physics of a grounded gate n-channel MOS transistor (ggNMOSt) is explained below. The explanation remains the same for grounded gate p-channel MOS transistor ggPMOSt except for the fact that the electrons should be replaced by holes.

#### ggNMOSt under two pin stress

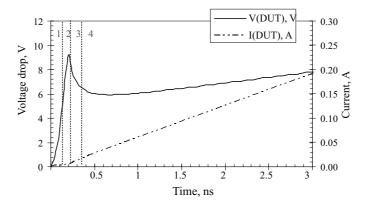

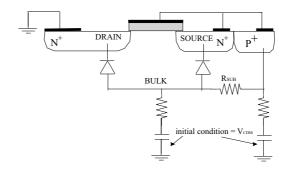

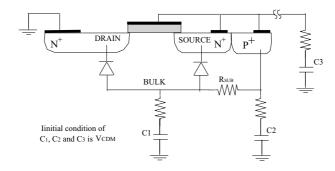

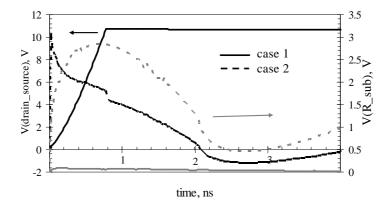

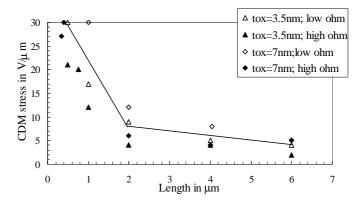

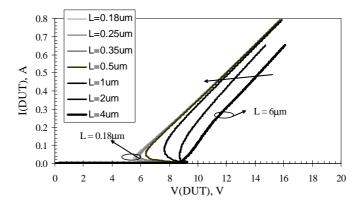

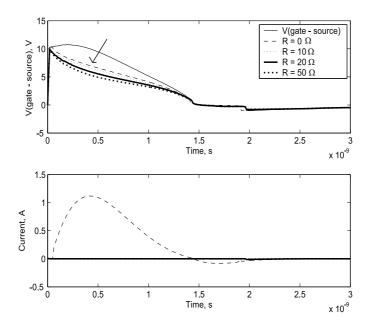

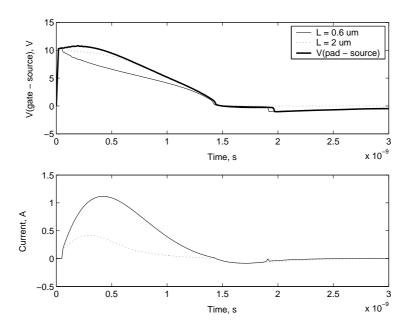

Two pin device behavior represents the device behavior when the stress is across two pins, namely the drain and source of the device. The layout of a ggNMOSt and the parasitic devices that become active when high current stress is applied across drain and source nodes of the ggNMOSt is shown in figure 3.3. When the drain is subjected to positive ESD stress with respect to source, a parasitic Lateral -Bipolar Junction Transistor (L-BJT) is activated. The operation of the L-BJT under ESD stress can be subdivided into four regions. The current and voltage transients across the device in these four regions are shown in figure 3.4.

1. As the voltage across the device is raised, the drain-bulk junction gets reverse biased and only the junction leakage current flows through substrate resistance  $R_{\rm SUB}$ .

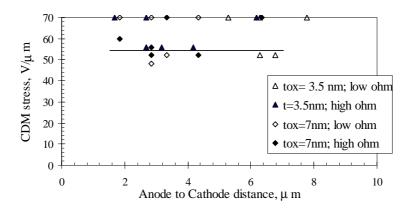

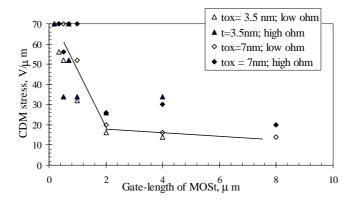

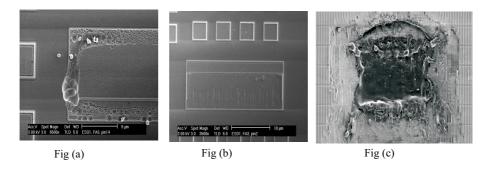

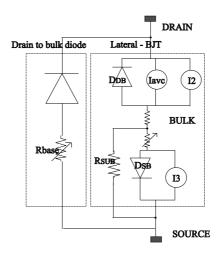

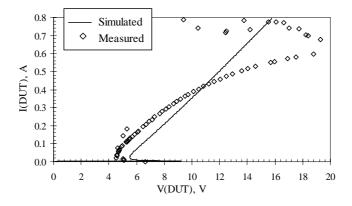

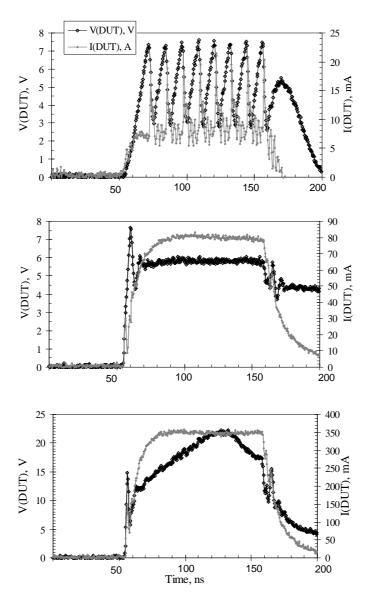

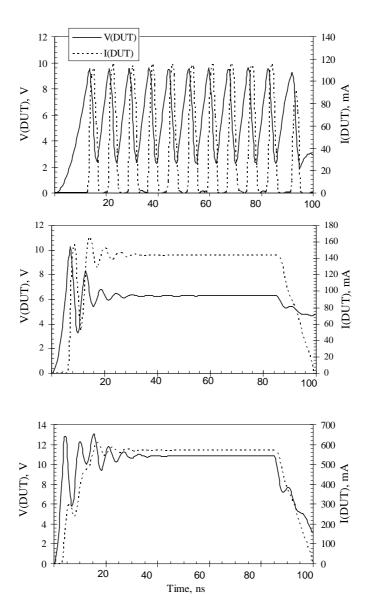

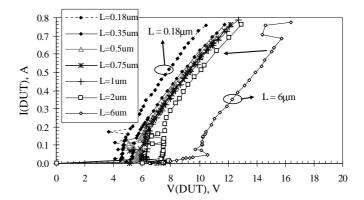

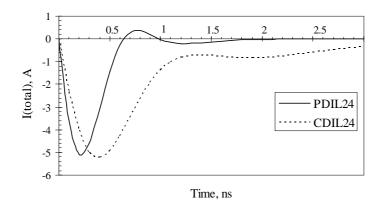

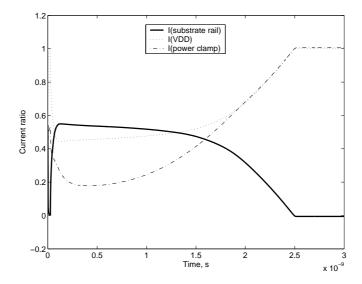

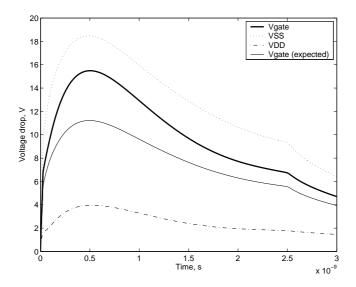

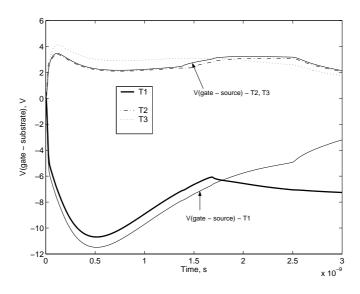

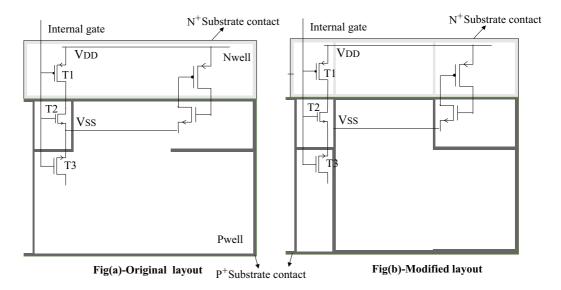

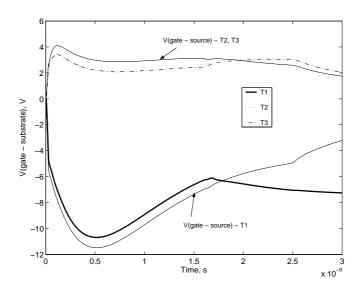

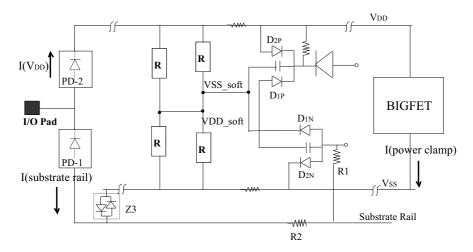

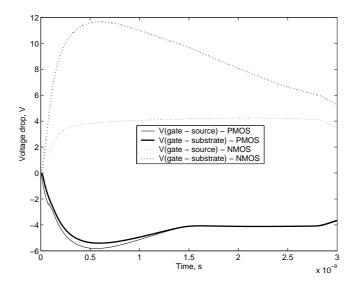

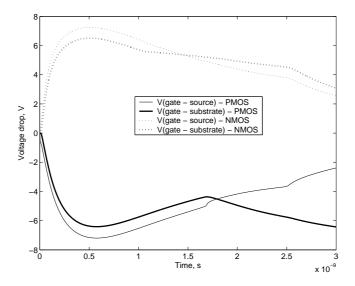

**Figure 3.4:** Current and Voltage transients across the ggNMOSt (L-BLT) in its different regions operation.